新通道达到 224Gbps 电气接口

高速电气 SerDes 应用不断发展。OIF 于 2016 年 8 月启动首个 112G-VSR 项目,并于 2017/18 年增加了多芯片模块 (MCM)、超短距离 (XSR)、中等距离 (MR) 和长距离 (LR)。2021 年,OIF 启动了两个 112G 线性和 112G 超短距离 (XSR)+ 的新项目。OIF 目前正在制定 CEI-224G 标准,以识别和定义典型系统中的下一代电气接口,用于通过背板/中间板或铜电缆在两个 PCBA 之间(甚至在两个机箱之间)的印刷电路板组件 (PCBA) 内的晶粒到晶粒、晶粒到 OE(光学引擎)、芯片到模块,以及芯片到芯片。

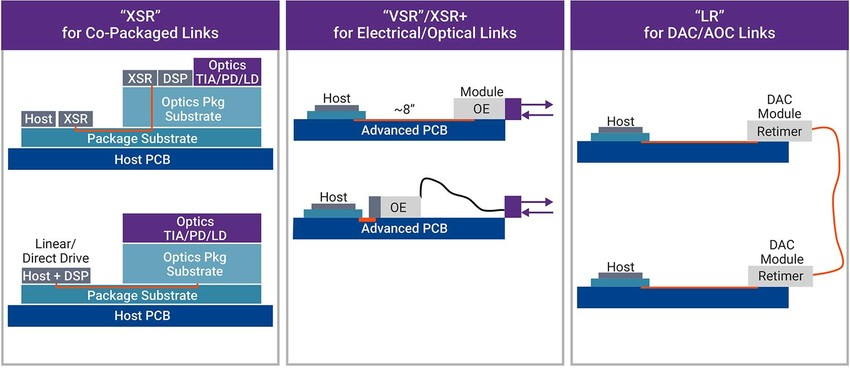

在类似线路中,IEEE 标准委员会最近批准了 IEEE P802.3df 项目授权请求 (PAR),以定义 200Gbps、400Gbps、800Gbps 和 1.6Tbps 电气接口的媒体访问控制参数、物理层和管理参数。工作组将为附件单元接口 (AUI) 和电气物理介质依赖 (PMD) 的 1/2/4/8 通道变体制定每通道 200Gbps 的电信号标准。 图 3:224Gbps 电气 SerDes 的早期用例

图 3:224Gbps 电气 SerDes 的早期用例

图 3 显示了 224Gbps 电气 SerDes 的早期用例,业界认为 102.4T 交换机和 800G/1.6T 相干光学模块将采用该案例,这些模块需要 224Gbps XSR/XSR+/VSR/LR SerDes。

224Gbps SerDes 架构

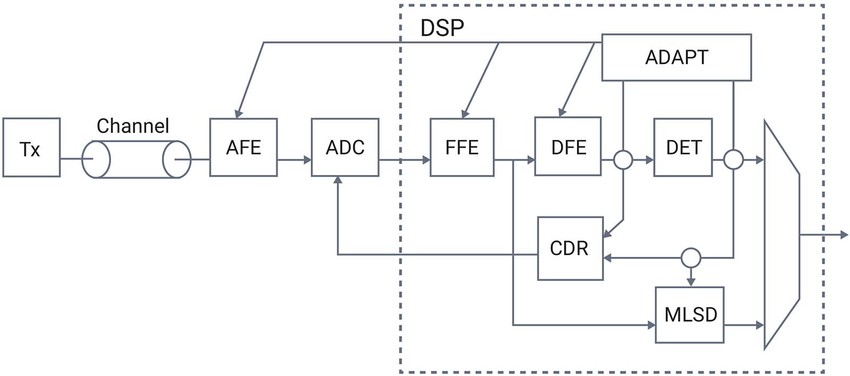

224Gbps 数据速率将单位间隔 (UI) 设计减少到逻辑延迟的序列。即使采用 PAM-6 调制,224Gbps 数据速率的 UI 也将约为 11ps。从 HPC 数据中心通道的演变角度考虑封装和 PCB 材料的改进/变化,很明显,224Gbps 收发器将需要灵活的高带宽 AFE,以扩展可用晶体管带宽的边界。 图 4:端到端 224Gbps 电气链路,突出显示接收器 DSP

图 4:端到端 224Gbps 电气链路,突出显示接收器 DSP

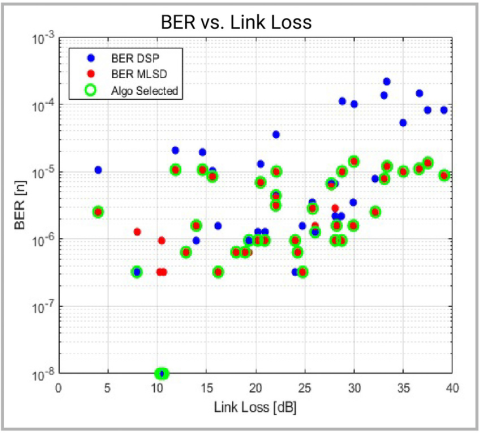

如图 4 所示,224Gbps 接收器必须具有自适应和差异化 DSP,才能在传统 VSR/MR/LR 通道中工作。使用 224Gbps 接口时,在某些信道上采用最大似然序列检测器 (MLSD)是一个常见的选项,但是,提高信道的比特误码率 (BER) 并不是一个魔法棒。图 5 显示了端到端 224G 发射器到接收器的仿真结果,与 BER 相比,实际 HPC 通道的链路损耗各不相同。 图 5:224Gbps 时的 BER 与信道损耗

图 5:224Gbps 时的 BER 与信道损耗

图 5 中的红点和蓝点表示具有或不具有 MLSD 的 BER。BER 跨信道损耗的分布和发散需要先进的 DSP 算法,该算法可在图中以绿点表示的信道损耗之间提供一致的 BER。

总结

需要 224G SerDes 来继续 HPC 数据中心的数据处理步伐。以太网已成为现代 HPC 数据中心服务器间通信的事实标准。因此,组织正在定义和开发包括 224Gbps 在内的下一代电气接口。新思科技提供完整的 200G/400G 和 800G 以太网控制器和 PHY IP 解决方案,包括物理编码子层 (PCS)、物理介质依赖 (PMD)、物理介质附件 (PMA) 和自动协商功能。虽然 800G 以太网和 1.6T 以太网的定义仍在进行中,但新思科技 的以太网 IP 解决方案已经在每端口带宽为224G SerDes的 800G/1.6T 早期方案中得到应用了。

0512-36805163

0512-36805163

电话:0512-36805163

电话:0512-36805163 邮箱:dp-sale@drapho.com

邮箱:dp-sale@drapho.com 地址:江苏省苏州市昆山市锦东路555号

地址:江苏省苏州市昆山市锦东路555号